실시간

뉴스

[테크다이브] 4년 만에 1.0→3.1단계로…AI 구현 핵심 'CXL'의 발전

[디지털데일리 고성현 기자] 바야흐로 인공지능(AI) 시대가 열리면서 반도체 업계는 몇가지 막중한 과제를 안게 됐습니다. 첫째는 인공 일반 지능(AGI) 구현을 위한 반도체 칩 성능 향상, 둘째는 막대한 데이터 처리량으로 인해 급증한 탄소배출 및 총소유비용(TCO) 절감이죠. 쉽게 말하면 AI 성능을 높이되, 더 적은 비용으로 이를 구현해야한다는 의미입니다.

이를 해결할 대안 중 하나인 컴퓨트익스프레스링크(CXL) 기술은 매우 빠른 속도로 성장해왔습니다. 익히 활용되는 기술이 아님에도 급속도로 용어가 널리 알려지고 있죠. 때때로 삼성전자, SK하이닉스가 CXL 메모리를 개발한다는 소식을 내놓으면서 'HBM에 이은 게임체인저가 되지 않을까?'라는 기대감까지 부풀게 하고 있습니다.

그렇다면 CXL은 무엇이고 어떤 과정을 거쳐 발전해 왔는지를 알아봐야겠죠. 우선 CXL의 의미부터 살펴봅시다. CXL는 프로세서와 장치 간 연결하는 방식에 대한 규약(Protocal)입니다. 데이터를 주고받고, 어떻게 처리할 것이냐를 정의한 인터페이스 표준이죠. (CXL이란? → [테크다이브] AI 성장에 컴퓨팅 부담 가중…CXL 기술로 한계 극복)

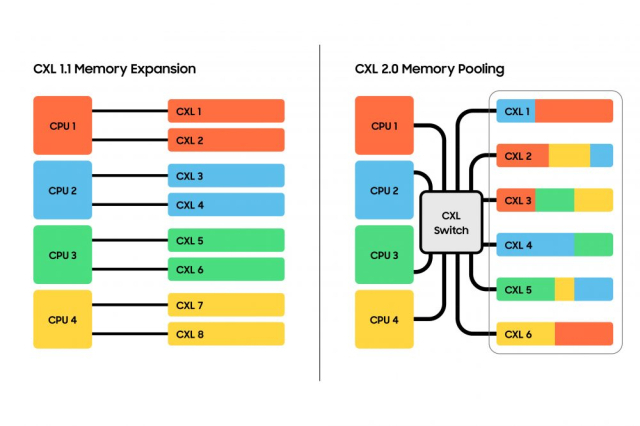

CXL 1.1과 CXL 2.0 구조를 비교하는 인포그래픽. CXL 1.1에서는 개별 CPU가 각각의 CXL 메모리 확장장치(Expander)와 연결되는 구조지만, CXL 2.0부터는 스위치를 통해 커다란 메모리 풀(Pool)에 접근할 수 있다. 다만 특정 CPU가 할당한 메모리 영역에는 타 CPU가 접근할 수 없는 한계가 있다. [ⓒ삼성전자 뉴스룸]

인텔이 2019년 제시하며 등장한 CXL 1.0은 호스트 프로세서에 연결된 메모리 용량 등을 확장하는 것에 집중했습니다. 기존 방식에서 CPU에 연결된 D램 모듈 개수는 한정적인데, 이 제한을 풀어냈다는 의미와 유사합니다. 비유하자면 자동차(Data)가 머무르는 주차장(D램) 크기가 커지고, 자동차들이 회사(CPU)로 가기 위해 이용하던 도로(Bandwidth, 대역폭)가 국도 크기에서 고속도로처럼 아주 크게 확장된 겁니다.

CXL 1.0의 문제점은 하나의 프로세서와 연결된 메모리를 다른 프로세서와 공유할 수 없다는 점입니다. 빅데이터·클라우드 등 막대한 데이터 양을 처리하려면 컴퓨팅 노드를 다중화하기 마련이지만, CXL 1.0은 단일 컴퓨팅 노드 내에서의 메모리 용량만을 확장할 수 있죠.

예를 들면 5명의 작업자(프로세서)가 A라는 거대한 프로젝트를 해야하는데, 각자 다른 작업대에서 일을 하는 상황인 겁니다. 이렇게 되면 서로가 얼만 작업했는지를 실시간으로 알기 어렵겠죠. 또 투입된 인원(비용) 대비 작업 효율이 떨어지고, 특정 작업자에게 과도한 업무량이 분배돼 과부하가 걸릴 수도 있습니다. 대학 시절 나만 억울하게 일해왔던 조별과제를 떠올려 보면 이해하기 쉬울 겁니다.

CXL 2.0의 핵심은 데이터를 저장하는 공간인 메모리를 풀(Pool)형태로 만드는 겁니다. 여러 프로세서가 접근할 수 있도록 해 효율을 높이는 거죠. 이 방식을 메모리 풀링(Memory Pooling)이라고 부릅니다. 메모리 풀링을 구현하려면 여러 프로세서를 하나의 메모리 풀과 연결해주는 스위치가 필요합니다. 따라서 CXL 2.0부터는 이들 장치를 CXL 규격으로 변환시키는 'CXL 스위치'가 탑재됩니다.

CXL 2.0이 되면 데이터센터의 모든 자원을 적재적소로 활용할 수 있을까요? 그렇진 않습니다. 대표적인 한계로 2가지를 꼽을 수 있는데요. 첫째는 CXL 2.0 시스템이 거대한 데이터센터 규모로 적용되기에는 확장성이 부족하다는 점, 둘째는 메모리 풀링 시스템 내 특정 프로세서가 할당한 영역을 타 장치가 들여다볼 수 없다는 점입니다.

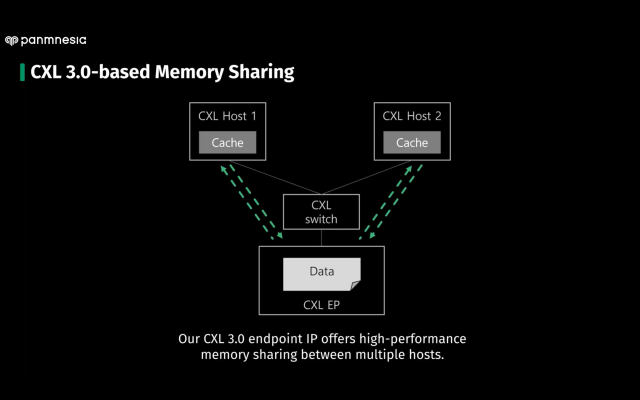

CXL 기반 메모리 공유에 대한 구조. CXL 호스트 간 캐시(Cache)의 일관성을 맞춰 데이터를 복사·이동 없이 실시간으로 공유할 수 있으며, 공동으로 작업해 효율을 극대화할 수 있다. [ⓒ파네시아 데모영상 갈무리]

따라서 이 두가지 문제를 가능케 해야만 데이터센터 내 CXL 시스템을 완벽히 구축할 수 있습니다. 이렇게 되면 불필요한 오버 프로비저닝(over-provisioning)이 발생하지 않고, 적재적소의 장치로 매우 빠른 데이터 처리가 가능하겠죠. 이같은 데이터 공유(Data Sharing)를 구현한 단계가 CXL 3.0, 그리고 CXL 3.1입니다.

CXL 3.0·3.1의 핵심은 CXL 시스템과 외부 메모리 등을 연결할 수 있는 멀티 레벨 스위치(Multi-level Switch)입니다. 호스트 당 여러개 타입의 장치를 같이 연결시킬 수 있어, 2.0에서의 랙(Rack) 단위보다 거대한 연결 규모를 갖출 수 있습니다. 한 프로세서에 할당된 메모리를 다른 프로세서가 실시간으로 접근해 작업할 수 있는 점도 지켜볼 대목입니다. 이를 통해 기존 데이터 전송 과정인 데이터 복사→이동(메모리 to CPU)→연산→재복사 후 저장 등의 흐름을 거치지 않고, 마치 내장된 캐시 메모리에서 연산하듯 빠른 속도로 접근이 가능하게 됐습니다.

2019년 제시된 CXL이 1.0에서부터 3.1까지 구현된 것은 불과 4년이라는 시간밖에 되지 않습니다. 가장 최신 단계인 3.1이 작년 하반기에 실리콘 검증(Silicon-proving)에 들어갔죠. 주목할 것은 CXL 2.0, CXL 3.0, CXL 3.1 원천 기술을 먼저 발표한 곳이 한국의 기업이란 점입니다.

2022년 설립된 반도체 스타트업 파네시아는 거대 글로벌 기업보다 빠르게 CXL 3.0, CXL 3.1 기술을 확보했습니다. 이는 창업자인 정명수 대표 겸 카이스트(KAIST) 교수의 연구 이력 덕분이죠. 정 대표는 2015년부터 연구팀과 함께 캐시 일관성(Cache Coherence), 데이터 공유를 연구해왔는데요. 2019년 발표된 CXL의 기반 기술이 정 교수가 집중하던 분야와 일치하면서 빠르게 빛을 발했습니다.

파네시아 등 반도체 기술 기업들의 노력으로 CXL 기술 발전은 급속도로 빠르게 이뤄졌지만, 이 기술이 데이터센터에 안착하려면 생각보다 오랜 시간이 필요할 듯 싶습니다. 원천 기술은 CXL 1.0부터 시작해 CXL 3.1까지 발전한 상황이지만, CXL을 구성하는 생태계가 그 속도를 따라잡지 못하고 있어서죠.

이 기술 주도권을 잡기 위한 거대 기업 간 물밑싸움도 영향을 주고 있습니다. CXL 생태계가 뒤처진 상황에서 차세대 표준이 정해지면 경쟁사에 밀릴 수밖에 없으니, 기술을 따라잡기 전까지 생태계 구성을 늦춰버리는 상황도 있는 거죠. 이는 우리가 CXL을 유심히 바라보고, 그 과정을 지켜봐야만 하는 이유 중 하나이기도 합니다.

Copyright ⓒ 디지털데일리. 무단전재 및 재배포 금지

이 기사와 관련된 기사

당신이 좋아할 만한 뉴스

오피니언

-

[DD퇴근길] 트럼프 주니어, 韓 찾는다…정용진 초청에 재계 총수 면담

2025-04-25 17:03:56 -

SKT, 해킹사태 수습 ‘시험대’...“진상규명은 아직, 이용자 보호 집중”(종합)

2025-04-25 14:45:57 -

신세계라이브쇼핑, 울릉도 관광 활성화 도모…“차별화된 여행 상품 운영”

2025-04-25 14:08:47 -

[일문일답] SKT “진상규명 기다려달라...2중 3중 이용자 보호 집중”

2025-04-25 14:02:03 -

[DD's톡] 'SKT, 카카오 지분 매각'에 양사 주가 희비 엇갈려

2025-04-25 11:31:10 -

SKT, 유심보호서비스 가입 폭증…최민희 "실질적 안전대책 필요"

2025-04-25 11:14:35

-

구글 모회사 알파벳, 1분기 '깜짝 실적'…광고 부문 성장 견인

2025-04-25 17:09:06 -

경주 개관 미디어아트 전시관, '덱스터' 자회사가 만든다

2025-04-25 16:39:44 -

[콘텐츠뷰] "겹사돈·전공의 미화 논란?"…정면돌파 택한 '언슬전생'

2025-04-25 16:02:21 -

'2초 노출에 2500만원'…웹툰 플랫폼, 콘텐츠 넘어 '광고 신시장' 연다

2025-04-25 15:59:30 -

MS, 혐한 논란에 사흘 만 공식 입장… “출시 지연에 사과”

2025-04-25 14:02:42 -

[DD's톡] 고개 못 드는 엔씨 주가… ‘아이온2’가 구할까

2025-04-25 13:54:28